RME Developer Story | Matthias Carstens

|

業界初の自社製コンポーネントによるオーディオ・ソリューションを実現 Fireface 800の開発を行っていた当時、FireWireでオーディオを扱うためのチップが、BridgeCo製のものしかありませんでした。彼らはオーディオだけでなく、ネットワークなどいろんなものをそこに詰め込もうとしたのですが、肝心のオーディオ部分のクォリティが私たちにとって十分ではありませんでした。そのため私たちは自分で開発することにしたのです。その結果、私たちは業界初の自社製コンポーネントによるFireWireオーディオ・ソリューションを提供することとなりました。 Fireface 800は、最高のパフォーマンスを発揮し、大きな成功を収めました。TC ElectronicsからDiceチップが登場するまで、競合製品は存在しませんでした。現在広く採用されているDiceチップは非常に優れたチップですが、私たちはよりフレキシブルで、自社の技術なのでさらに発展する可能性を秘めています。ただ、Fireface 800にはひとつ問題がありました。FireWireの物理的なチップは当時Texas Instruments(TI)社製のものを使用していたため、私たちはFireWireプロトコルの最後のパートにアクセスする手段がありませんでした。そこへ2008年にAppleから新しいコンピュータがリリースされるのですが、そこにはAgereというFireWireチップが使用されていました。そこにはバグがあり、TI製のチップとだけうまく動作することができませんでした。我々にはどうすることもできず、突如としてFireface 800はAppleのコンピュータに対応しなくなってしまいました。

その後のファームウェアのアップデートにより、問題は解消するのですが、こうした経緯もあり、Fireface UCでUSBに対応する際には、このようなことが二度と起こらないように配慮しました。RMEのUSBオーディオ・ソリューションでは、すべての処理がFPGA内で行われます。そのため、もし将来またバグの多いチップが現れたとしても、ファームウェアのアップデートで対応することができます。これはFireWireでも同じです。Fireface UFXでは、Fireface 800のコードを基に、Agereチップへの互換性を含めて問題をフィックスしたファームウェアを搭載しました。これもプログラム可能なFPGAの利点の一つです。

Fireface UFXに搭載された革新的な機能の数々 私たちはもちろんマーケットのトレンドを観察しているのですが、最近他のメーカーがユニットにエフェクト機能を搭載し始めていることに気づきました。基本的に彼らは正しいです。Windowsコンピュータはどんどん速くなっていますが、レイテンシーは10年前とさほど変わっていません。ボーカルにリバーブをリアルタイムに掛けようとしたら、ユニットの中にリバーブ機能があった方が好都合です。そこで私は、DAM-1を作った優秀なDSPプログラマに、UFXのプロジェクトへ合流してもらうことにしました。ということでUFXは4人の開発者が一緒に関わった最初の製品となりました。 そして、それぞれの開発者が専門の分野—USBインターフェイスやFireWireインターフェイス、FPGA、デジタル・ミキシングとエフェクト、MacとWindows用のソフトウェア—といった分野で力を存分に発揮した結果がFireface UFXなのです。 エフェクト機能についてはマーケットの動向に対するRMEからの回答でもあるのですが、DURec™(Direct USB Recording)については全く新しいコンセプトで「私たちは小さな会社だけど、大きな会社にはこんなことできないだろ?」というために搭載しました(笑)。 (右上段へ続く) |

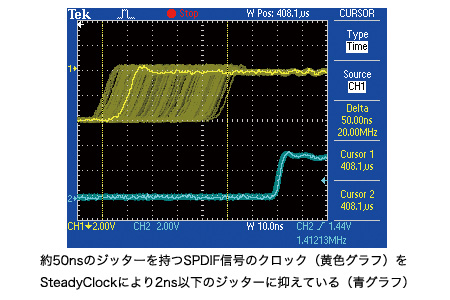

RMEが誇る「SteadyClock」の優位点 SteadyClockの優位点は2つあります。1つは、完全にFPGAの中だけで動作し、ほんのわずかのリソースしか消費しない点です。非常に効率的です。2つめは、動作がすごく速く、ふらつかないということです。他の製品のことを悪く言いたくはないのですが、例えばとある有名なテクノロジーと比較すると、SteadyClockの開発を始めた当時、彼らはスーパー・フィルターでそれを実現していました。つまり、非常に素早くロックされるのですが、ジッターの低減は行われず、最終的にロックされるまでに10〜15秒程度かかっていました。また、周波数が少し変わっただけでアンロックされ、再ロックしなければならず、このときにクリック・ノイズが発生していました。 なので、私たちは、すぐにロックできる仕組みを考えることにしました。その完璧な前例は、古いADATレコーダーにありました。ADATレコーダーのピッチ・フェーダーは、素早く上げ下げしても1サンプルも取りこぼさずに追随しました。これをリファレンスにして開発を進め、SteadyClockができあがったのです。 SteadyClockは、カタログなどで謳っているようにデジタルでジッター・リダクションを行います。2.4 kHzで30 dB程度、それより高い周波数ではさらに低減されます。SteadyClockのリリース時には、FPGA内で200 MHzのDDSクロックを使用していました。当時、私の記憶では多分Apogeeの製品だったと思うのですが、一番高価なDDSチップでも100 MHzが最速でした。私たちはすべて自分たちでデザインしていますので、たまに、チップ・メーカーが考えもしないようなものを作ることができるんです(笑)。 現在は、SteadyClockは800 MHz(Fireface UFX)で動作しています。ことさらそこを強調したりはしていないのでほとんどの人は知らないと思いますが、Fireface UFXなどは内部的にはそのように動作しています。

内部には通常の水晶を使用しており、基準のリファレンスは50 MHzです。FPGAによりこれを200 MHz、さらにFireface UFXのケースでは800 MHzに変換し、DDSシステム全体がこれを基に動作します。信号が入力されると、デジタル・フィルターによりスキャニングそしてフィルタリングされ、アナログPLLにより平坦化されます。200 MHzでは2.5ナノ秒ごとに処理を行い、アナログPLLがそれを整えてから出力します。とてもシンプルな仕組みです。 |